At DAC 2024, Altair showcased its 3D-IC design and SimLab multi-physics modelling and simulation tool. Today, the company has announced the acquisition of Metrics Design Automation, a Canadian company led by Joe Costello , former CEO of Cadence Design Systems (1988-1997). The company described DSim as a full feature System Verilog and VHDL RTL simulator. It enables designers to simulate ...

EDA and IP

Accellera announces Federated Simulation Standard working group

DAC 2024: Accellera Systems Initiative, the EDA standards body, reflects the industry’s shift of focus from chip to systems, with the formation of a new working group. The Federated Simulation Standard (FSS) working group will focus on the Interoperability of simulators, models, and other components that together form systems-of-systems simulation environments, said Martin Barnasconi, Accellera’s technical committee chair and chair ...

NoC design tool is cloud-based

DAC 2024: Believed to be the first cloud-based NoC (network on chip) design tool, the iNoCulator is available on an early access basis from SignatureIP. Today, there is a need to design multiple chipets and design scalable designs with chiplet-based systems, explained Purna Mohanty, CEO of SignatureIP. As the interconnect between compute, storage, memory and I/O blocks on a chip, ...

Siemens EDA for Intel 16 and 18A nodes

Siemens Digital Industries Software and Intel Foundry have certified Solido EDA software for Intel’s 16 and 18A nodes and enabled an embedded multi-die interconnect bridge (EMIB) that can help customers leverage the performance, space and power efficiency advantages of 3D-IC (3D integrated circuit) designs more quickly. Intel 18A is the latest node in Intel Foundry’s process technology roadmap, featuring RibbonFET ...

EDA industry benefits from new markets

DAC 2024: The EDA industry is reaping the rewards of an evolution in the semiconductor and software industries, said Jay Vleeschhouwer, software research analyst at Griffin Securities (pictured). The essential nature of EDA has become more apparent, he said, as semiconductor companies are becoming increasingly like systems companies and systems companies are becoming increasingly like semiconductor companies, he said. Software ...

Synopsys’ Sashi Obilisetty is honoured at DAC 2024

The executive director of R&D in Synopsys’ EDA group, Sashi Obilisetty, was presented with the Marie R. Pistilli Women in Engineering Achievement Award at this year’s DAC in San Francisco, California. The award recognises individuals who have “significantly helped advance women in electronic design”. This year’s recipient is an entrepreneur, founding DualSoft in 1998, focusing on RT analysis, which was ...

RISC-V Summit: SiFive’s 4th generation embedded cores

SiFive announced the 4th generation of RISC-V CPU cores for embedded applications at RISC-V Summit Europe 2024 today. There are eight cores, three of which are 32bit while the other five are 64bit. To trade performance against power and area, their pipelines will span two-stage single-issue, to eight-stage dual-issue – see the table below. They are all covered by the ...

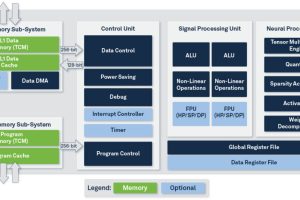

AI processor intellectual property aimed at TinyML

Ceva has announced a neural network processing core aimed at SoCs needing to run TinyML models. There are two versions: NPN32 with 32 int8 MACs NPN64 with 64 int8 MACs “Both of which benefit from Ceva-NetSqueeze for direct processing of compressed model weights,” according to the company. “NPN32 is optimised for most TinyML workloads targeting voice, audio, object detection and ...

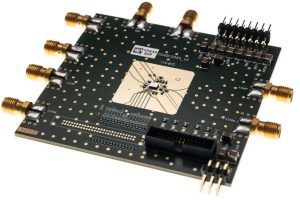

VLSI Symposium: RF ADCs cover 5GHz

At the IEEE VLSI Symposium this week, Imec revealed two ADCs for 5GHz ‘beyond 5G’ communication, one for base stations and one for phones. The base station ADC operates over bands up to 5GHz. It is a 10Gsample/s cmos hierarchical time-interleaved ADC that delivers 9 ENOB (effective number of bits) at low frequencies and 8.2 ENOB at Nyquist. SFDR (spurious-free ...

Chiplet Summit: Alphawave tapes out UCIe multi-interface chiplet

On TSMC’s 7nm process, Alphawave Semi has taped-out an IO chiplet covering UCIe (universal chiplet interconnect express – rev1.1) Ethernet, PCIe and CXL, claiming it to be industry’s first. “Delivering a total bandwidth of up to 1.6Tbit/s, the enables up to 16 lanes of multi-standard PHY supporting PCIe 6.0, CXL 3.x and 800G Ethernet in a combination of mixed operating ...

Electronics Weekly Electronics Design & Components Tech News

Electronics Weekly Electronics Design & Components Tech News