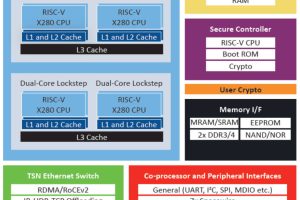

There are eight cores, three of which are 32bit while the other five are 64bit.

To trade performance against power and area, their pipelines will span two-stage single-issue, to eight-stage dual-issue – see the table below.

They are all covered by the companies ‘Essential’ range branding, and SiFive is claiming “up op 40% runtime power reduction” compared with its third generation Essential processors.

Can the it elaborate on this?

“The power reduction is not achieved through one big change, but is the cumulative effect of many small improvements and optimizations throughout the design,” the company told Electronics Weekly. “In addition more advanced, finer grained power and clock gating is employed, together with new RAM retention features and DVFS [dynamic voltage and frequency scaling) support.”

How much energy?

“We cannot provide actual power consumption numbers, due to the large number of factors that can influence this across different applications,” said SiFive.

| SiFive RISC-V Gen4 cores | Low power and area 2-3 stage single-issue |

8 stage single-issue | High performance 8 stage dual-issue |

| 64bit application processor | U6 Gen4 | U7 Gen4 | |

| 64bit real-time embedded | S2 Gen4 | S6 Gen4 | S7 Gen4 |

| 32bit real-time embedded | E2 Gen4 | E6 Gen4 | E7 Gen4 |

U6 and U7 Gen 4 cores will execute the RVA22 instruction set and will support a hypervisor for separated code execution.

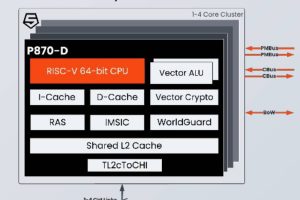

All the gen 4 cores get SiFive/RISC-V WorldGuard hardware-based support for a trusted execution environment, as well as secure debug.

AMBA ACE bus is supported on the memory port of all but the E2 and S2 cores.

All except U6 and U7 cores have RISC-V’s Zcmp and Zcmt compressed code extensions.

Beyond this are few details so far, except that there will be support for embedded Linux, FreeRTOS, Eclipse C/C++/ IDE

Electronics Weekly Electronics Design & Components Tech News

Electronics Weekly Electronics Design & Components Tech News