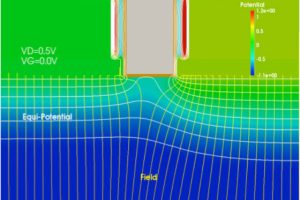

“More than 50% reduction of the statistical variability compared to bulk mosfets with identical dimensions”, is the claim of Glasgow-based Semiwise for its ‘flat field transistor’, which “is complemented by 30% performance increase and 5% reduction of the manufacturing costs compared to the equivalent bulk CMOS technology transistors.” The company is aiming its flat field transistor (right) at the sense ...

EDA and IP

MathWorks updates MATLAB and Simulink

MathWorks has released 2022a of the MATLAB and Simulink product families. Release 2022a (R2022a) offers hundreds of new and updated features and functions in MATLAB and Simulink along with five new products and 11 major updates. New capabilities in MATLAB include new apps and App Designer functions, graphics enhancements, and the ability to customize Live Editor tasks. Simulink updates enable users to streamline masking workflows with ...

STEM holds the potential for a fairer future

Caroline Hayes talks to Renu Mehra, R&D group director for Synopsys’ Digital Design Group, about encouraging girls to study STEM and pursue their passion. The Marie R Pistilli Award honours an individual who has contributed to advancing the profile of women in electronic design automation (EDA) or creating opportunities for women in the industry. Some recipients have been leaders within ...

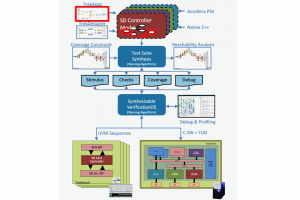

Open standard for RISC-V verification is announced at DVCon

At this year’s (virtual) functional design and verification conference, DVCon US 2022, the RISC-V Verification Interface (RVVI) was announced by Imperas Software. The interface is available at github. The draft open standard defines “a number of interfaces required to bring together several of the subsystems required for RISC-V processor design verification”. Components based on the open standard can be re-used across ...

Framework simplifies specification model based on uvm

At DVCon US this week, Breker Verification Systems has announced SystemUVM, a framework which simplifies specification model composition for test content synthesis. It uses a universal verification methodology (uvm) /SystemVerilog syntactic and semantic approach to drive test content synthesis and uses AI planning algorithms for deep sequential bug hunting in existing uvm environments, said the company. Adopting a coverage-driven approach ...

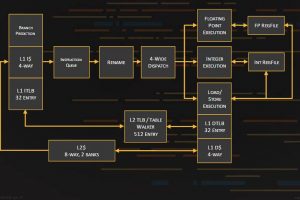

SiFive puts its whole Risc-V processor range into Intel’s foundry service

Risc-V processor IP company SiFive is partnering with Intel Foundry Services (IFS) to optimise SiFive IP for Intel’s foundry customers. The two companies have already collaborated, using SiFive’s ‘Performance P550‘ processor and Intel PCIe and DDR interfaces to build the ‘Horse Creek’ Risc-V development platform. “We’re excited to extend our relationship with IFS to ensure the full SiFive Risc-V processor portfolio ...

Viewpoint: Who wins in the Sonos v Google smart speaker patent dispute?

Sonos alleged that Google’s smart speaker devices infringed its US patents, and the ITC has agreed. But who will be the winner from this patent dispute, asks Michael Jaeger, a partner and patent attorney at Withers & Rogers? Following the conclusion of a long-standing legal battle, Sonos has emerged victorious to block the import into the US of Google’s smart speaker ...

CES: BMW picks Green Hills for electric car

BWM has picked Green Hills’ software for control units in its iX all-electric vehicle. Integrity real-time operating system is used in the digital instrument cluster, head-up display, driver camera system, surround view and parking assistant. Software developers, according to Green Hills, used its Multi integrated development environment, and ASIL-qualified compilers and run-time libraries for both Integrity and AutoSar Classic operating ...

TrekApp tool tests stress in SoC and processor designs

Verification and stimulus specialist, Breker Verification Systems, has taken its Cache Coherency TrekApp as the basis for the System Coherency Synthesis TrekApp, which it introduced at DAC58 in San Francisco. The tool uses abstract models of common and novel algorithms to automatically generate high coverage coherency tests for complex, multi-agent system platforms based on coverage directives. The TrekApp can be configured ...

eFPGA soft IP provides options for SoC and ASIC designs

At DAC, French embedded FPGA (eFPGA) supplier, Menta, introduced what it claims is the first eFPGA soft IP. It enables designers to perform closure directly at the top level. This is significant for AI, as well as space and defence projects, which rely on low latency, explained Yoan Dupret, Menta’s managing director and CEO. Since 2013, Menta’s technology has ...

Electronics Weekly Electronics Design & Components Tech News

Electronics Weekly Electronics Design & Components Tech News