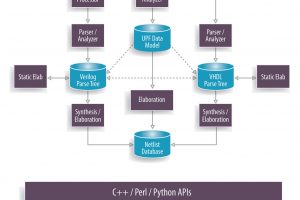

To gain at least an 18 month advantage in getting a product to market, Verific Design Automation builds SystemVerilog, UPF and VHDL parser platforms which accelerates the production cycle because the RTL front end is immediately accepted by the semiconductor industry, says the company. It offers parsers, analysers and elaborators for SystemVerilog IEEE 1800-2005 / 2009 / 2012 / 2017, ...

EDA and IP

A new look at the figures around Moore’s law

Joe Sawicki , executive vice president, IC EDA at Siemens, challenged the mutterings that Moore’s law has run its course, and said the semiconductor industry was blighted with pessimism. At this year’s DAC (Design Automation Conference) he set about looking at the figures in a new light. “There have been morose expectations and miserable prognostics, for like 20 years,” he reasoned, ...

UK made: Register memory IP cuts SoC power for wearables

Sheffield memory design house SureCore is offering intellectual property to cut register file power consumption. Branded MiniMiser, its architecture is based on a customised storage element – rather than on the foundry bit cell – and exploits the company’s SRAM power saving techniques. Multi-port and high-performance variants can be generated. “MiniMiser gives developers a new way of optimising the power envelope ...

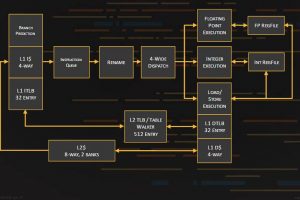

SiFive claims ‘fastest licensable RISC-V processor IP’ for its 11+SPECInt2006/GHz core

SiFive has created what “is expected to be the fastest licensable RISC-V processor IP core in the market”, when it emerges in 2022. Building on the earlier Performance P550 processor, company engineering estimates are that it will have 40% more performance per clock cycle – to 11+SPECInt2006/GHz – and it has architecture enhancements improve maximum clock frequency – together adding ...

Design rules for functional safety are explored at DAC

The role of EDA tools to automate manipulating, storing and exchanging data for functional safety systems was in the spotlight at DAC, as engineers wrestle with ways to improve interoperability, traceability and automation. The Accellera Functional Safety Working Group was created in December in 2019 and is dedicated to standardise across system, module, component and IP levels to define an ...

FPGA foundation sets up for disruption at DAC

Following its created in April this year, the Open Source FPGA Foundation was at DAC (Design Automation Conference) to advocate for innovation with open source tools and wrestle control from what has been a largely unchanged FPGA space for 30 years. The fledging non-profit foundation has over 20 members from academia and more than 1,000 individual members worldwide, said CEO, ...

Imagination offers Risc-V core IP

Imagination Technologies has announced Risc-V CPU intellectual property for SoC companies. Branded Catapult, it is a “product line designed from the ground-up for next-generation heterogeneous compute needs,” according to Imagination. “Leveraging Imagination’s 20 years of experience in delivering complex IP solutions, Catapult CPUs can be configured for performance, efficiency or balanced profiles.” There will be four families: dynamic microcontrollers real-time ...

Complete camera-to-cloud people counting eval kit

Analog Devices has introduced a evaluation kit for people-counting using one of its DSPs. In a case and designed to be attached to a ceiling looking straight down, the kit includes a camera and everything needed to get the counted data to the cloud. Its main ingredients are a particular DSP from its Blackfin range, the ADSPBF707BBCZ4-EGE, and a people counting ...

In-field programmer gets external branding options

Segger is offering custom versions of its Flasher Portable Plus stand-alone in-field programmer, “enabling corporations to supply their service technicians with a branded tool”, it said, Visual custom options include injection moulding the case in different coloured plastic and printign logos and slogans on the outside. The display content, for example changing the splash screen, can also be changed. “The ...

sureCore memory IP in Semidynamics’ RISC-V chip

SureCore, the Sheffield low-power memory IP house, has designed a power and area efficient, high performance, multi-port, embedded memory solution for Semidynamics’ new RISC-V-based, tensor processing chip. Semidynamics is developing a high bandwidth, vector processing unit optimised for tensor processing aimed at AI applications. In order for AI to realise its full performance potential, the speed at which tensors are ...

Electronics Weekly Electronics Design & Components Tech News

Electronics Weekly Electronics Design & Components Tech News