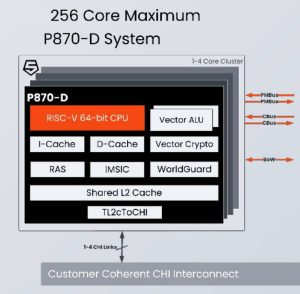

Called P870-D, it is an update of the non-data centre P870, with support added for AMBA CHI protocol.

“By harnessing a standard CHI bus,” said SiFive, “the P870-D enables SiFive’s customers to scale up to 256 cores while harnessing industry-standard protocols including CXL [Compute Express Link] and CHI C2C [chip to chip] to enable coherent high core count heterogeneous SoCs and chiplets.”

Like P870, P870-D has a six-wide out-of-order core implementing the RVA23 RISC-V profile with vectors and vector crypto.

The earlier core did not have a CHI bridge nor cross-cluster RAS (reliability availability serviceability) protections for data integrity, and only stretched to 32 core coherent clusters.

For functional safety and security, P870-D also gets a distributed scalable IOMMU for accelerating virtualised device IO, and it has RISC-V’s Sv57 extension to support a 57bit virtual address space.

Network-on-chip

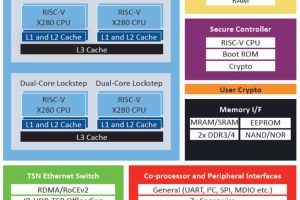

In a collaboration with Arteris, the company has created an AI workload design example with P870-D processors linked to SiFive’s X280 RISC-V cores – which are optimised for machine learning inferencing – connected with Arteris’ network-on-chip.

“Network-on-chip IP helps streamline the process of building complex, multi-core heterogeneous SoCs to accommodate AI workloads,” said Arteris CMO Michal Siwinski.

Software

“Many of the foundational open source software elements already exist for RISC-V and this momentum is accelerating due to the collaborative efforts across the community such as the RISE Project. P870-D is aligned with the standards defined by RISC-V international,” said SiFive. “Customers can leverage SiFive’s standard run-control debug capabilities, along with supported debugging solutions from tool vendors.”

For security, the company has its WorldGuard model for trusted execution environments.

P870-D is sampling now, with a production release scheduled before the end of this year.

Electronics Weekly Electronics Design & Components Tech News

Electronics Weekly Electronics Design & Components Tech News