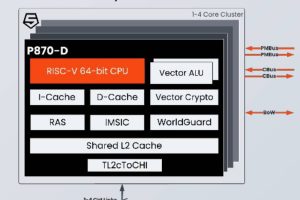

SiFive has announced RISC-V core intellectual property for data centre processors. Called P870-D, it is an update of the non-data centre P870, with support added for AMBA CHI protocol. “By harnessing a standard CHI bus,” said SiFive, “the P870-D enables SiFive’s customers to scale up to 256 cores while harnessing industry-standard protocols including CXL [Compute Express Link] and CHI C2C [chip ...

Tag Archives: SiFive

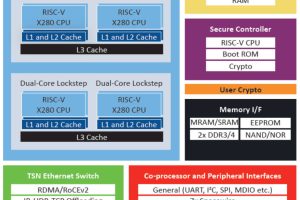

Microchip goes 64bit with RISC-V, and plans Arm

Microchip has announced its first 64bit processors, picking the RISC-V instruction set for the initial parts: an octa-core for space and a industrial quad-core. Although, “future PIC64 families will include devices based on RISC-V or Arm architectures”, said the company. PIC64-HPSC is the family name of the space processors, which have come out of a 2022 deal with NASA to ...

RISC-V Summit: SiFive’s 4th generation embedded cores

SiFive announced the 4th generation of RISC-V CPU cores for embedded applications at RISC-V Summit Europe 2024 today. There are eight cores, three of which are 32bit while the other five are 64bit. To trade performance against power and area, their pipelines will span two-stage single-issue, to eight-stage dual-issue – see the table below. They are all covered by the ...

Qualcomm and Google to develop RISC-V for wearables

Qualcomm is to create RISC-V based silicon for wearables, working with Google to optimise it for Google’s Wear OS. “We are excited to extend our work with Qualcomm Technologies and bring a RISC-V wearable solution to market,” said Google general manager Bjorn Kilburn. Leading up to this, the companies will continue to invest in Snapdragon Wear platforms for the Wear ...

SiFive’s high-performance RISC-Vs for AI and machine learning

SiFive has announced a pair of high-end RISC-V cores for AI and machine learning in consumer, automotive and infrastructure markets. “Performance P870 and Intelligence X390 offer a new level of low power compute density and vector compute capability, and when combined provide performance for data intensive compute,” according to the company, which is advocating combining the general-purpose scalar P870 with ...

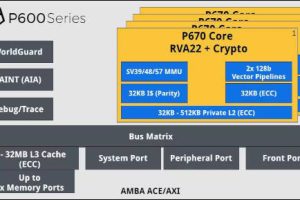

High-performance RISC-V cores from SiFive

SiFive has announced two high-performance RISC-V processing cores. “P670 and P470 are specifically designed for the most demanding workloads for wearables and other advanced consumer applications,” said SiFive v-p Chris Jones. “We have optimised these RISC-V Vector-enabled products to deliver performance and efficiency improvements and we are in evaluations with a number of top-tier customers.” Both are also available in ...

Functional safety dev tools for E6-A and S7-A automotive RISC-V cores

IAR Systems is aiming at SiFive’s E6-A and S7-A automotive RISC-V cores with its latest iteration of Embedded Workbench. “E6-A series is aimed at a variety of real-time 32bit applications, from system control to hardware security modules, safety islands and stand-alone in microcontrollers,” according to IAR. “S7-A is a 64bit, high-performance real-time core suited to the needs of modern SoCs ...

SiFive has licenses C++ library for Risc-V

IC intellectual property company SiFive has licensed Segger’s emRun++ C++ library for Risc-V, a library optimised for GCC/LLVM-based tool chains and embedded systems, based on the emRun and emFloat runtime and floating-point libraries. This follows on from last year, when SiFive licensed Segger’s emRun C runtime library for use in its Risc-V IDE and Tool packages. “It was an easy ...

SiFive opens Cambridge R&D centre

SiFive has opened a UK R&D centre in Cambridge. The company plans to hire over 100 people. “As part of our global expansion, we’re proud to open our UK R&D Centre in Cambridge to access the considerable local technical talent, especially CPU experts,” said Patrick Little, CEO and Chairman, SiFive, “with long-term plans to grow talent and teams in Cambridge and ...

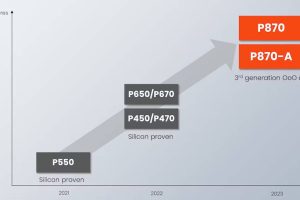

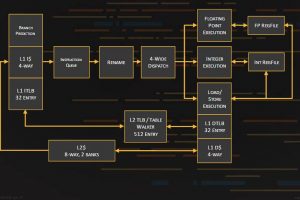

SiFive claims ‘fastest licensable RISC-V processor IP’ for its 11+SPECInt2006/GHz core

SiFive has created what “is expected to be the fastest licensable RISC-V processor IP core in the market”, when it emerges in 2022. Building on the earlier Performance P550 processor, company engineering estimates are that it will have 40% more performance per clock cycle – to 11+SPECInt2006/GHz – and it has architecture enhancements improve maximum clock frequency – together adding ...

Electronics Weekly Electronics Design & Components Tech News

Electronics Weekly Electronics Design & Components Tech News