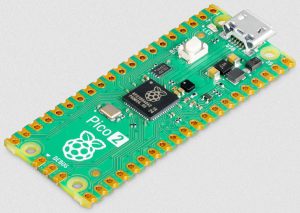

Not initially available on its own (ETA pre-year-end), it will first ship as part of the Raspberry Pi Pico 2 single-board microcontroller (right) – which is the same 21 x 51mm size as the original Pico, and priced from $5.

The four cores are independent on the silicon, but only two can be enabled at any one time for operation.

“Each of CPU0 and CPU1 can be independently selected to be an Arm or RISC-V processor at boot time. So: two Arms, two RISC-Vs or one of each – not sure that’s [the latter] going to be a common use case,” Raspberry Pi CEO Eben Upton told Electronics Weekly. “When you write a UF2 file into flash, the boot ROM will auto-detect the architecture of the binary and choose the right cores to run it. The chip comes with all cores enabled, and you can choose to permanently disable one or other architecture by writing OTP bits.”

The Arm cores are 150MHz versions of the more powerful Cortex-M33 (up from the 133MHz Cortex-M0+ pair in the RP2040), and for its RISC-V Raspberry Pi has chosen the open-source Hazard3 3-stage processor, which executes the RV32I instruction set, and optional extensions.

Cortex-M33 is the security-enhanced Cortex-M3, which has the microcontroller version of Arm’s TrustZone, to the RP2350 adds: signed boot, 8kbyte of anti-fuse one-time memory for key storage, SHA256 acceleration, a hardware true random number generator and glitch detectors.

“These features, including the secure boot ROM, allow professional users to integrate RP2350, and Pico 2, into products with confidence,” according to Raspberry Pi.

How much of the on-die security infrastructure can the RISC-V cores make use of?

“Everything is available except for: Cortex-M33 internal peripherals like the SAU, Cortex-M33 co-processors like the RCP, and boot rom support for secure boot,” Hazard3 RISC-V architect Luke Wren told Electronics Weekly. “So features like AccessCTRL bus filtering, AccessCTRL GPIO filtering and DMA channel assignment are all free to use.”

Wren works for Raspberry Pi, and has details of Hazard3 on his GitHub. Did he create Hazard3 first, and then it was decided to add it to RP2350?

“Broadly yes”, said CEO Upton. “Though perhaps some of the focus on extensions – especially for code density – was motivated by the need to squeeze stuff into the boot ROM.”

Moving to Cortex-M33 also brings with it 32bit multiply and divide, and a move to the ARMv8-M instruction set (from Armv6-M).

Alongside the cores, the RP2350 IC has 520kbyte of SRAM. As with the earlier RP2040, there is no on-die flash, but the Pico 2 board adds a 4Mbyte QSPI flash IC. Versions with co-packaged serial flash are planned.

Peripherals include 2x UART, 2x SPI controllers, 2x I2C controllers, 24x PWM channels, a USB 1.1 controller (and PHY) with host and device support, and 12 of the company’s ‘PIO’ peripheral state-machines.

This is similar to Raspberry Pi’s first MCU, RP2040, except that the earlier part had only 16 PWM channels and eight PIOs.

There is also a high-speed data peripheral, called HSTX, which can output 300Mbit/s from GPIO.

Of the 26 GPIO pins on the Pico 2, four can also be used as ADC inputs.

Operation is over 1.8 to 5.5Vdc, and -20°C to +85°C. Unlike the RP2040, RP2350 has a number of low-power states.

Programming is expected in C, C++ and Python, all of which will be supported with documentation.

Raspberry Pi Pico 2 will be available individually, or in reels of 480, and “Raspberry Pi Pico 2 will remain in production until at least January 2040,” said the organisation.

Editor: With Raspberry Pi’s reputation for thorough software support and documentation, this IC and its ecosystem could make an excellent platform on which to learn about TrustZone security hardware, or the RISC-V architecture.

Find the Hazard3 RISC-V core on the ‘Wren6991’ GitHub

See also: A little look at RP2040’s programmable i-o state-machines

Electronics Weekly Electronics Design & Components Tech News

Electronics Weekly Electronics Design & Components Tech News