ST has joined Quintauris, the RISC-V facilitator, as its sixth shareholder alongside Bosch, Infineon, Nordic Semiconductor, NXP and Qualcomm. Quintauris was founded in December 2023 to advance the adoption of products based on RISC-V principles. This will include access to reference architectures, and assistance in the creation of versatile, cross-industry solutions. The initial core industry applications will be for the ...

Tag Archives: RISC-V

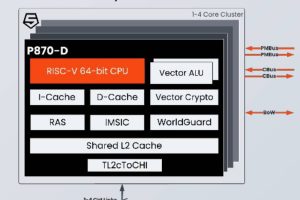

RISC-V cluster IP for data centre SoCs and chiplets

SiFive has announced RISC-V core intellectual property for data centre processors. Called P870-D, it is an update of the non-data centre P870, with support added for AMBA CHI protocol. “By harnessing a standard CHI bus,” said SiFive, “the P870-D enables SiFive’s customers to scale up to 256 cores while harnessing industry-standard protocols including CXL [Compute Express Link] and CHI C2C [chip ...

Akeana reveals its RISC-V cores

Akeana has announced a little about its RISC-V processor intellectual property. There will be three series: 100 Series – configurable 32bit RISC-V cores for embedded microcontrollers 1000 Series – includes 64bit RISC-V cores and a memory management unit, optional support for multi-threading and extensions including: vector, hypervisor and AI computation. 5000 Series – 64bit RISC-V cores optimised for laptops, data ...

New Raspberry Pi MCU – RP2350 – Risc-V, Arm and security

Raspberry Pi has announced its second microcontroller, the RP2350, adding two RISC-V cores alongside improved Arm cores, more ram, and security. Not initially available on its own (ETA pre-year-end), it will first ship as part of the Raspberry Pi Pico 2 single-board microcontroller (right) – which is the same 21 x 51mm size as the original Pico, and priced from ...

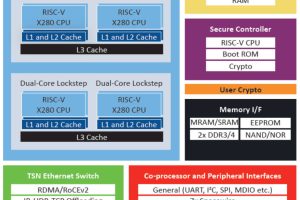

Microchip goes 64bit with RISC-V, and plans Arm

Microchip has announced its first 64bit processors, picking the RISC-V instruction set for the initial parts: an octa-core for space and a industrial quad-core. Although, “future PIC64 families will include devices based on RISC-V or Arm architectures”, said the company. PIC64-HPSC is the family name of the space processors, which have come out of a 2022 deal with NASA to ...

RISC-V Summit: SiFive’s 4th generation embedded cores

SiFive announced the 4th generation of RISC-V CPU cores for embedded applications at RISC-V Summit Europe 2024 today. There are eight cores, three of which are 32bit while the other five are 64bit. To trade performance against power and area, their pipelines will span two-stage single-issue, to eight-stage dual-issue – see the table below. They are all covered by the ...

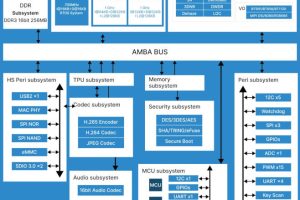

One I missed: Arm Cortex-A53, 2x Risc-V and 8051 – all on the same chip

Shenzhen MilkV Technology has a chip that combines: 1x 1GHz C906 RISC-V CPU 1x 700MHz C906 RISC-V CPU 1x 1GHz Arm Cortex-A53 CPU 1x 8051 CPU 1x 1Top/s (INT8) neural processor Called SG2002, it also has 256M (byte, probably…) DRAM, a camera interface, video acceleration, an audio codec and a crypto engine. Peripherals include 100Mbit/s Ethernet (with a phy), USB 2.0, ...

Embedded Studio support for general-purpose RISC-V MCU

Renesas has increased support for its first RISC-V-based general-purpose microcontrollers by integrating Segger’s Embedded Studio into version 1.1.0 of Renesas’ RISC-V Smart Configurator code generator for R9A02G021 group MCUs. Smart Configurator is a graphical tool that generates source code that will configuring peripherals such as timers, interfaces and interrupt controllers. In this case, the source code is ready to be ...

Embedded World: fast 64bit quad core RISC-V development board for Linux

SiFive has announced a quad-core RISC-V development board. HiFive Premier P550, as it will be known, is built around an Eswin EIC7700 processor which has SiFive’s 64bit three-issue, out-of-order P550 cores, 256kbyte L2 cache and 4Mbyte L3 cache. It is collaborating with Canonical to ensure Ubuntu will run on the board, which is similar to a PC motherboard. “The board ...

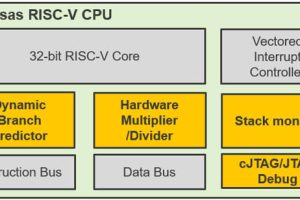

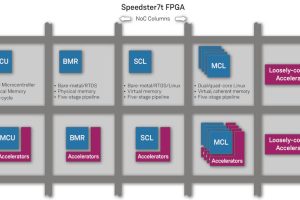

Linux-capable RISC-V soft cores for Achronix FPGAs

Achronix has teamed up with Bluespec to offer a family of Linux-capable RISC-V soft processors for the Speedster7t FPGA family. “Bluespec’s RISC-V processors now integrate into the Achronix 2D network-on-chip architecture, simplifying integration and enabling engineers to add scalable processing to their designs,” according to Achronix. “The network allows multiple instances of the RISC-V core to be added, and relocated ...

Electronics Weekly Electronics Design & Components Tech News

Electronics Weekly Electronics Design & Components Tech News