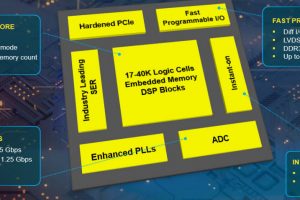

Lattice Semiconductor has released the second family of devices developed from its Nexus 28nm FDSoI platform, equipping them with fast PCI Express (PCIe) and Gigabit Ethernet interfaces for co-processing, signal bridging, and system control. Certus-NX FPGAs, as they will be known, are intended to be general purpose, aimed at applications from data processing in automated industrial equipment to system management ...

FPGA / PLD

The latest Electronics Weekly product news on FPGA (field-programmable gate array) and PLD (programmable logic device) devices to be (re)configured by a user after manufacturing.

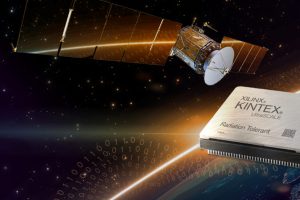

Reconfigurable architecture prepares for nascent space era

Travel to planets as well as working among the stars and lower orbits, are seeing renewed levels of interest and activity. Today, there are estimated to be 366bn commercial satellites and SpaceX, a private company is currently planning to launch the Falcon 9 rocket and NASA’s Crew Dragon spacecraft on 27 May. One of the major challenges in the space ...

Lattice picks FD-SOI and redesigns FPGAs for embedded vision and edge AI

Lattice has switched to 28nm FD-SOI (fully-depleted silicon-on-insulator) technology for a range of sram-based FPGAs intended for embedded vision and artificial intelligence processing in industrial, automotive and consumer systems. Although they are ram-based, and therefore need to boot from adjacent memory, the firm has found a way to get chip outputs enabled, set and stable within 3ms of power-up – allowing ...

Adaptable, flexible and open source: the wish list for young engineers

The working practices of today’s young engineers are very much on Victor Peng’s mind. The president and CEO of Xilinx explained why the company’s Vitis, the software platform announced at the Xilinx Developers’ Forum in San Jose, California. He conceded that the company has not normally been associated with open source products. Now it is offering Vitis. “The new generation ...

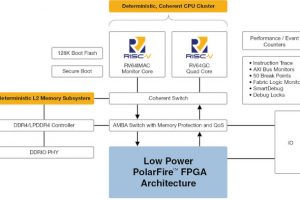

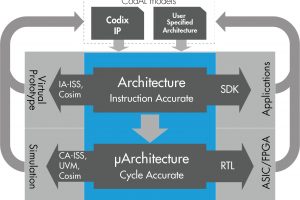

Risc-V day: Microchip adds Risc-V hard IP to PolarFire FPGAs

Microchip detailed an FPGA family with a quad core 64bit RISC-V processor alongside the programmable array. Called ‘PolarFire SoC’, the “architecture brings real-time deterministic asymmetric multiprocessing capability to Linux platforms in a multi-core coherent CPU cluster”, according to the firm, which worked with Risc-V specialist SiFive to create the devices. Real-time operation is included for safety-critical, system control and trusted ...

Xilinx puts new life into HTC and AI development

Xilinx embraces open source community and introduces the Vitis software platform for hardware and software development. At this year’s Xilinx Developers Forum, the company introduced the Vitis software platform, which tailors the hardware architecture to the software of algorithm code without intervention. President and CEO, Victor Peng, explained that the unified platform was developed to “empower software developers, with the ...

Intel shipping Stratix 10

Intel is shipping Stratix 10 DX FPGAs which are designed to support Intel Ultra Path Interconnect (Intel UPI), PCI-Express (PCIe) Gen4 x16, and a controller for Intel Optane memory to provide acceleration. Stratix 10 DX FPGAs with the new interfaces include the option to support select Intel Optane DC persistent memory DIMMs. They increase bandwidth and provide coherent memory expansion and ...

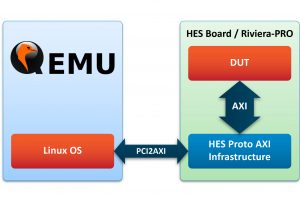

Aldec enhances verification and validation tool

Aldec improves its HES Proto-AXI software to provide greater support hardware verification and software validation.

Intel ships 10nm Agilex FPGAs

Intel begins shipments of the first Agilex FPGAs to early access program customers.

A view from the RISC-V Summit

The RISC-V Summit was held in Santa Clara, California, USA this week (3 – 6 December). The industry looked ahead to the potential of the open architecture and was a platform for the providers of core IP and development tools that make up its ecosystem. There were two announcements from IAR Systems in support of establishing a robust ecosystem for ...

Electronics Weekly Electronics Design & Components Tech News

Electronics Weekly Electronics Design & Components Tech News