There were two announcements from IAR Systems in support of establishing a robust ecosystem for RISC-V. The first was with IP provider, SiFive, to collaborate on bringing the former’s compiler and debugger tools to the configurable processor core IP.

Integration of tools and IP is expected to support developers to deliver products and to increase deployment of the open, free instruction set architecture (ISA).

Anders Holmberg, Chief Strategy Officer, IAR Systems, said the aim is to help developers boost productivity and focus on innovation. “SiFive is a leader in commercial RISC-V core IP, and our toolchain IAR Embedded Workbench is the most widely used toolchain for building embedded applications,” he said. The accent is on scalable, efficient custom silicon and development tools to meet compute workloads.

IAR Embedded Workbench for RISC-V will be available mid-2019. The toolchain claims to offer “leading code quality, size and speed” as well as an integrated debugger with simulator and hardware debugging support.

The software company also announced a partnership with CPU IP provider, Andes, to support the company’s RISC-V cores, the AndesCore N25(F)/NX25(F) and A25/AX25, in IAR Embedded Workbench for RISC-V. The first version will be available in mid-2019. AndeStar V5 instruction extension and Andes Custom Extension (ACE) instruction customisation capabilities will be coupled with Workbench to maximise code speed and minimise code size for RISC-V cores.

Automation and real-time computing

The latest version of its tool suite and a new EOSC-V core optimised for Linux and real-time computing were announced by Codasip.

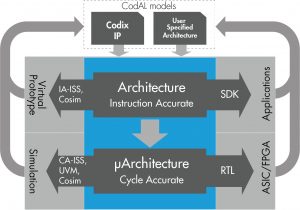

Its Studio 8 tool suite allows developers to write a high-level description of a processor and automatically synthesises the design (pictured).

“As the RISC-V ISA specification evolves and adds an ever-increasing number of optional architecture extensions, a processor design methodology that allows for both rapid architectural exploration and simplified creation of easily implementable RTL becomes essential,” observed Chris Jones, Vice President of Marketing at Codasip. “What is needed is a high-level processor description language optimised for RISC-V,” he added, introducing the tool suite.

The processor description is written in CodAL, an architecture description language, and then the design’s RTL, test bench, virtual platform models and processor software development kit (C/C++ compiler, debugger, profiler) are automatically synthesised. The methodology reduces the time spend maintaining a complete software development kit (SDK) by using an instruction accurate (IA) processor model in CodAL to Time that would otherwise be required to maintain a complete SDK and implementation is significantly reduced thanks to the methodology that uses an instruction accurate (IA) processor model in CodAL for SDK generation and a cycle accurate model for implementation.

New functionality and features for the eighth generation tool suite include support for an LLVM debugger and OpenOCB, Studio/CodeSpace integrated development environments (IDEs) based on Eclipse Oxygen and more interactive consoles and improvements to the test suites and verification to support user-defined RISC-V extensions.

The company also introduced the 64-bit Bk7 processor, adding to the Bk family. It has a seven-stage pipeline with branch prediction, optional full memory management unit (MMU) with virtual addressing support for operating systems such as Linux, popular RISC-V standard extensions and industry standard external interfaces.

It is the company’s highest-performance processor to date and is customisable for developers to add instructions, registers or interfaces.

Studio 8 and the Bk7 processor will be generally available Q1 2019, with early access to selected customers immediately.

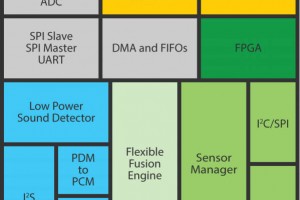

Microchip announced that it is adding what it believes to be the industry’s first RISC-V SoC FPGA architecture to its Mi-V ecosystem. The FPGAs combine Microsemiconductor PolarFire FPGAs and a microprocessor sub-system based on the RISC-V ISA.

Ahead of the Summit, the Linux Foundation announced its collaboration with the RISC-V Foundation to accelerate open source development and adoption of the RISC-V ISA.

Electronics Weekly Electronics Design & Components Tech News

Electronics Weekly Electronics Design & Components Tech News