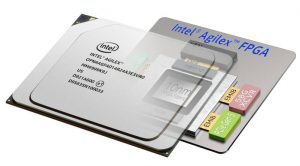

Participants in the early access program include Colorado Engineering, Mantaro Networks, Microsoft and Silicom. These customers are using Agilex FPGAs to develop solutions for networking, 5G and accelerated data analytics.

On average, Intel claims, designs running in the fastest speed grade of Agilex FPGAs achieve a 40% improvement in maximum clockspeed compared to the same designs running in the most popular speed grade of Stratix 10 devices (-2 speed grade), tested February 2019.

Agilex FPGAs consume up to 40% lower total power compared with Intel Stratix 10 FPGAs. The company derived these figures from benchmarking an example design suite comparing total power estimates of each design running both FPGAs. These power estimates were also tested in February 2019, using the Stratix 10 early power estimator and an internal Intel analysis and architecture simulation and modelling.

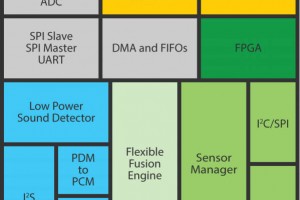

Each Intel Agilex DSP block can perform two FP16 floating-point operations (FLOPs) per clock cycle. The total FLOPs for FP16 configuration is derived by multiplying 2x the maximum number of DSP blocks to be offered in a single Intel Agilex FPGA by the maximum clock frequency specified for that block.

Intel says its Agilex FPGAs are the only FPGAs which support hardened BFLOAT16, with up to 40 teraflops of digital signal processor performance. They are also able to scale for higher bandwidth compared to the previous generation and support up to 112Gbps data rates for networking requirements for 400GE and beyond. The FPGAs additionally support current DDR4, along with the upcoming DDR5, HBM and Intel Optane DC persistent memory.

“The Intel Agilex FPGA product family leverages the breadth of Intel innovation and technology leadership, including architecture, packaging, process technology, developer tools and a fast path to power reduction with eASIC technology” said Intel senior vice president and general manager of the networking and custom logic group, Dan McNamara.

Electronics Weekly Electronics Design & Components Tech News

Electronics Weekly Electronics Design & Components Tech News