The electronic design automation (EDA) industry is benefiting from the evolution of the semiconductor industry in which the lines between systems and semiconductors are becoming meshed together. According to Jay Vleeschhouwer, software research analyst at Griffin Securities, the introduction of AI/machine learning (ML) and engineering software has been a driving force, together with the universality of EDA, which can be used by newly addressable markets such as automotive (see News: EDA industry benefits from new markets) .

The electronic design automation (EDA) industry is benefiting from the evolution of the semiconductor industry in which the lines between systems and semiconductors are becoming meshed together. According to Jay Vleeschhouwer, software research analyst at Griffin Securities, the introduction of AI/machine learning (ML) and engineering software has been a driving force, together with the universality of EDA, which can be used by newly addressable markets such as automotive (see News: EDA industry benefits from new markets) .

Thermal design

Siemens was particularly proactive at this year’s DAC. It introduced Calibre 3DThermal, which analyses the thermal performance of a chip and package design. Chips are impeded by heat, as resistivity and transistor behaviour changes with temperature, explains John Ferguson, senior director, Calibre Product Management at Siemens Industry Software.

Temperature changes power behaviour and mechanical stresses by default when stacking and when drilling a TSV (through silicon via) in the structure. The heat has to be quite high for several hours, which affects the transistor behaviour, he explains.

The physical verification tools examine inside the die and its electrical connections, enabling a chiplet designer to check that the design is behaving electrically as intended.

The tool addresses design and verification from early stage chip and 3D assembly exploration to final sign-off. It requires only minimal inputs to begin feasibility analysis, says Ferguson, and adopts a progressive approach to later perform more detailed analyses considering metalisation details and their impact on thermal performance as more detailed information becomes available.

3D-IC innovation

A custom version of Siemens’ Simcenter Flotherm software solver engine creates chiplet-level thermal models for static or dynamic simulation of full 3D-IC assemblies for IC to system thermal modelling from IC to package to board to system level, says the company. Debugging is via the traditional Calibre RVE software results viewer.

Ferguson provides a customer example of how CEA (formerly CEA-Leti) reduced a design’s simulation process of days to less than one hour. The software has also been verified and certified by Intel Foundry for its processes.

The company also announced that United Microelectronics Corporation has deployed a thermal analysis flow for customers powered by Calibre 3DThermal and tailored for its wafer-on-wafer and 3D-IC technologies.

3D-IC design

Ansys has adopted Nvidia Omniverse APIs (application programming interfaces) for use with its physics solver products, that is, HFSS, Icepak and RedHawk-SC, to provide real-time visualisation for 3D-IC designs. Denser 3D-ICs complicate design challenges related to electromagnetic issues as well as heat and stress management. 3D multi-physics visualisation can help designers to understand the interaction between components and interact with 3D models to evaluate and find the origins of problems, says the company. It envisages optimised designs will deliver faster data rates, increase functionality and improve reliability for 5G/6G, IoT, AI/ML, cloud computing and autonomous vehicles.

Ansys has also announced that RedHawk-SC uses Nvidia’s Omniverse for design simulation and is powered by its Grace CPU superchip.

Ecosystem

Intel foundry also provided an update on its design ecosystem. Ansys, Cadence, Siemens and Synopsys announced reference flows for Intel’s EMIB (embedded multi-die interconnect bridge) advanced packaging technology.

Ansys is working with Intel Foundry to deliver sign-off verification of thermal and power integrity and mechanical reliability of EMIB assembly technology, while Cadence has announced availability of a complete EMIB 2.5D packaging flow, digital and custom/analogue flows for Intel 18A, and design IP for Intel 18A. Synopsys has announced the availability of its AI-driven multi-die reference flow for Intel Foundry’s EMIB packaging.

Intel is currently shipping EMIB chips with 55µm and 45µm bump pitches. Gary Patton, corporate vice-president, GM design enablement, confirms its roadmap is to produce 40µm chips in 2025 and 36µm EMIB chips in 2026.

Siemens announced its EMIB reference flow for Intel Foundry’s customers, driven by an Intel Foundry package assembly design kit and using its Calibre nmPlatform to validate EMIB silicon layouts for design rule checking, layout versus schematic (LVS) physical verification and 3DThermal analysis. The company also offers the Solido Simulation Suite certification for custom IC verification on Intel 16, Intel 3 and Intel 18A nodes.

Chiplets

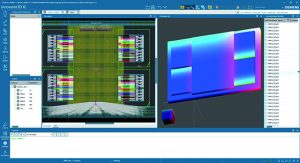

Siemens also introduced Innovator3D IC software for planning and heterogeneous integration of asics and chiplets using a digital twin of the semiconductor package assembly.

It uses hierarchical device planning for complex 2.5/3D integrated designs with millions of pins. It encompasses power, signal, thermal and mechanical stress analysis tools for rapid ‘what-if’ exploration. It also identifies challenges before the detailed design implementation phase, saving rework efforts, says Siemens.

Designs are represented as geometrically partitioned regions with attributes controlling elaboration and implementation methods. Critical updates can be quickly implemented while matching analytic techniques to specific regions, to avoid “excessively long execution times”. Hierarchical interface route path planning optimises chiplet interfaces and pin assignments.

Asic, chiplet and interposer implementation are achieved using the company’s Aprisa software digital IC place and route technology, Xpedition Package Designer software, Calibre 3DThermal software, NX software for mechanical design, Tessent Test software and Calibre 3DSTACK software for interchiplet DRC (design rule checking), LVS physical verification and tapeout sign-off. Its open architecture also supports integration with third-party point solutions. Industry standard formats supported include 3Dblox, LEF/DEF, Oasis and interface IP protocols, such as UCIe and BoW.

Adding AI for verification

The increased complexity of semiconductor designs that need validating is a problem for simulators, says Pradeep Thiagarajan, principal product manager for custom IC verification, introducing Siemens’ automated electrostatic discharge (ESD) checking tool for ICs. Solido Simulation Suite software (Solido Sim), is an integrated suite of AI-accelerated Spice, Fast Spice and mixed-signal simulators for design and verification of analogue, mixed-signal and custom IC designs.

Solido was originally a custom IC verification tool, but as the industry moves past finfet and on to ‘gate all around’ packages, the increasing complexity merits a tool with RF capabilities and a partitioned FastSpice simulator with an AI engine to bolt on to Spice products, explains Thiagarajan.

It supports full-chip level verification, with context-aware checks that allow design teams to verify ESD paths quickly and in time to secure waivers from foundry rules that can lead to smaller die sizes and optimised designs, says the company.

Siemens’ Innovator3D-IC uses hierarchical device planning to address increasingly complex 2.5/3D integrated designs

The context-aware ESD verification checks compliance against foundry rules across all phases of IC design, says the company. It points out that foundry ESD rules may be overly conservative, however, so detailed transistor-level breakdown models are used to identify at-risk paths with Spice-level precision.

Integrating dynamic simulation results from Solido into a full-chip Calibre PERC result determines if designs are electrically robust. If there are any circuit errors, Solido identifies netlists and devices that need to be improved.

The context-aware IC design verification features automated voltage propagation, voltage-aware design rule checking and the integration of physical and electrical information within a logic-driven layout framework.

There are three new simulators in the suite: Solido Spice, Solido FastSpice and Solido LibSpice, all powered by Solido Sim AI, which the company describes as circuit simulation using algorithms that are self-verifying and tuned to Spice accuracy. [This could be more accurately described as machine learning and is claimed to improve acceleration by orders-of-magnitude using existing foundry-certified device models without alteration.]

NoC news

Cadence Design Systems announced the addition of Janus network on chip to its system IP portfolio. The Tensilica RTL generation tool uses packetised messages to achieve better use of wires, to reduce wire count and accelerate timing closure. It can be used with the company’s simulation and emulation hardware and software tools as well as its Special Performance Analysis tool to explore the design’s architecture to mitigate routing congestion and timing issues around complex SoC interconnects before physical implementation. Built-in power management, clock domain crossing and width matching reduce design complexity to configure small sub-systems to full SoCs and there is the potential for it to be used for multi-chip systems in the future. It is compatible with any IP with an industry-standard interface, including AXI4 and AHB.

* Read more DAC news online:

NoC design tool is cloud-based

Synopsys’ Sashi Obilisetty is honoured

Accellera announces FSS working group

Focus shifts for HDL workflow in chiplet era

Yorchip predicts 2026 will be the year of the chiplet

Electronics Weekly Electronics Design & Components Tech News

Electronics Weekly Electronics Design & Components Tech News