At the 61st DAC, it was clear that the software and silicon worlds are not colliding but meshing together, bringing opportunities for tools to address the challenges complex chip design presents. By Caroline Hayes. The electronic design automation (EDA) industry is benefiting from the evolution of the semiconductor industry in which the lines between systems and semiconductors are becoming meshed ...

Tag Archives: EDA

IoT security considerations for EDA

Electronic design automation tools have a role to play in designing secure options for the IoT, says Samudrapom Dam. The IoT has revolutionised different industries, enabling advanced industrial systems, autonomous vehicles and smart homes. As IoT devices become increasingly prevalent, ensuring their security has become crucial. IoT devices are more susceptible to attacks and security threats because security solutions compatible ...

Altair to acquire Metrics Design Automation

At DAC 2024, Altair showcased its 3D-IC design and SimLab multi-physics modelling and simulation tool. Today, the company has announced the acquisition of Metrics Design Automation, a Canadian company led by Joe Costello , former CEO of Cadence Design Systems (1988-1997). The company described DSim as a full feature System Verilog and VHDL RTL simulator. It enables designers to simulate ...

Accellera announces Federated Simulation Standard working group

DAC 2024: Accellera Systems Initiative, the EDA standards body, reflects the industry’s shift of focus from chip to systems, with the formation of a new working group. The Federated Simulation Standard (FSS) working group will focus on the Interoperability of simulators, models, and other components that together form systems-of-systems simulation environments, said Martin Barnasconi, Accellera’s technical committee chair and chair ...

NoC design tool is cloud-based

DAC 2024: Believed to be the first cloud-based NoC (network on chip) design tool, the iNoCulator is available on an early access basis from SignatureIP. Today, there is a need to design multiple chipets and design scalable designs with chiplet-based systems, explained Purna Mohanty, CEO of SignatureIP. As the interconnect between compute, storage, memory and I/O blocks on a chip, ...

Focus shifts for HDL workflow in chiplet era

DAC 2024: The need to organise HDL hardware description language) tools in an era of chiplet design and higher abstraction and higher synthesis levels, Sigasi has introduced its Visual HDL portfolio, designed to correct inefficient HDL-based design workflows and reduce the number of iterations needed. The Belgium company explained that SVH (Sigasi Visual HDL) is an IDE (integrated development environment) ...

EDA industry benefits from new markets

DAC 2024: The EDA industry is reaping the rewards of an evolution in the semiconductor and software industries, said Jay Vleeschhouwer, software research analyst at Griffin Securities (pictured). The essential nature of EDA has become more apparent, he said, as semiconductor companies are becoming increasingly like systems companies and systems companies are becoming increasingly like semiconductor companies, he said. Software ...

Synopsys’ Sashi Obilisetty is honoured at DAC 2024

The executive director of R&D in Synopsys’ EDA group, Sashi Obilisetty, was presented with the Marie R. Pistilli Women in Engineering Achievement Award at this year’s DAC in San Francisco, California. The award recognises individuals who have “significantly helped advance women in electronic design”. This year’s recipient is an entrepreneur, founding DualSoft in 1998, focusing on RT analysis, which was ...

DVCon USA 24-27 February 2025

DVCon 2025 is a highly technical conference for design and verification with discussions on the latest technologies and how they can be adopted for projects and designs.

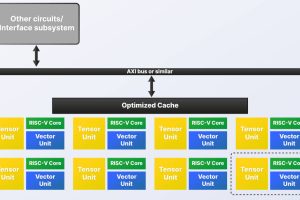

Semidynamics proposes modular RISC-V architecture for scalable AI processing

Barcelona-based Semidynamics is aiming at next-generation AI chips and algorithms such as transformer with intellectual property called ‘All-In-One AI’. Rather than having on the same IC a multi-core CPU, a multi-core GPU for vector processing and a multi-core neural processor for tensor processing, it is advocating multiple instances of a block consisting of one out-of-order 64bit RISC-V CPU, one (GPU-like) ...

Electronics Weekly Electronics Design & Components Tech News

Electronics Weekly Electronics Design & Components Tech News