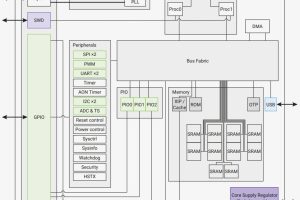

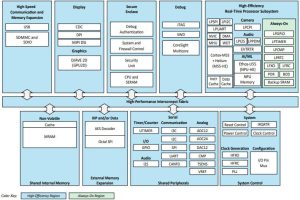

Three dual-issue, 32-bit CPU core complexes enable the microcontroller to support applications including electric DC motor control, aerospace engines, and Ethernet and CAN FD connectivity, plus automotive applications that require compliance with SIL-1 and ASIL-D functional safety requirements.

The microcontroller features two independent Power Architecture z7 cores offering up to 300 MHz operation, and a single z7 core operating in lockstep with one of the main computational cores. The two main cores offer signal processing extension instruction support for digital signal processing, and 16 Kbytes of I-cache and 16 Kbytes of D-cache. The microcontroller offers 8 Mbytes of on-chip flash memory, in addition to 512 Kbytes of on-chip general purpose RAM (including 64 Kbytes of standby RAM).

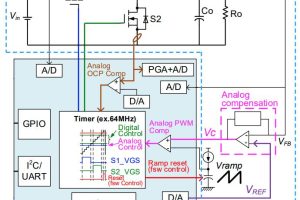

The device’s two enhanced queued analogue-to-digital converter (eQADC) modules provide support for 70 analogue input pins, or up to 182 inputs using off-chip mutiplexers. On-chip security encryption protection using a tamper detection module and cryptographic services.

The NXP MPC5777C Power Architecture microcontroller is supported by the MPC5777C-DEVB development board, which enables the development of both hardware and software for applications such as battery management systems, traction motor control, and internal combustion engines and transmissions. The development board includes an MPC5777C microcontroller together with MC33FS6520LAE System Basis Chip (SBC) and the TJA1100 and TJA1145T/FD Ethernet and CAN FD PHY transceivers.

Electronics Weekly Electronics Design & Components Tech News

Electronics Weekly Electronics Design & Components Tech News