Cloud-based FPGA design is the focus of a tie-up between Xilinx and IBM. IBM’s cloud service will host the Xilinx SDAccel development environment which will allow developers to describe their algorithms in OpenCL, C, and C++ and then compile directly to Xilinx FPGA-based acceleration boards. This is an open access cloud service, called SuperVessel, which can be used by application developers, ...

FPGA / PLD

The latest Electronics Weekly product news on FPGA (field-programmable gate array) and PLD (programmable logic device) devices to be (re)configured by a user after manufacturing.

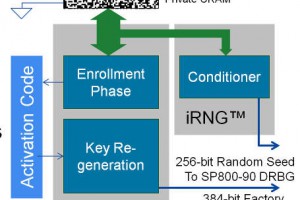

Cryptographic keys protect production FPGAs, says Microsemi

Microsemi has introduced a secured production programming capability for its FPGAs. The firm uses hardware and software to generate and inject cryptographic keys and configuration bitstreams into its FPGAs as a preventative measure against cloning, reverse engineering, malware insertion or leakage of sensitive intellectual property (IP). Called SPPS, the security package includes the use of “customer” and “manufacturer” hardware security ...

Xilinx: finfets deliver 56G PAM4 transceiver

Xilinx, has developed 16nm finfet-based 56G transceiver technology using the 4-level pulse amplitude modulation (PAM4). “PAM4 solutions will help drive the next wave of Ethernet deployment for optical and copper interconnects by doubling bandwidth on the existing infrastructure,” said the firm. The company’s 56G PAM4 transceiver technology has been developed to tackle physical limitations of data transmission at such line ...

Kit for getting started with secure FPGA design

Avnet has updated its design software offering for Microsemi’s SmartFusion2 KickStart development kit to offer a data security demonstration. The kit, sold exclusively through Avnet, is an entry-level development platform designed to facilitate prototyping using Microsemi’s SmartFusion2 system-on-chip FPGAs. The development board integrates a single event upset (SEU)-immune SmartFusion2 SoC FPGA, a secure and integrated programmable device with 10,000 logic ...

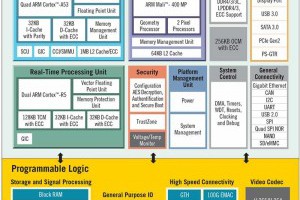

Xilinx ships 16nm Virtex

Xilinx is shipping a 16nm finfet Virtex UltraScale+ FPGA made on TSMC’s 16FF+ process. Xilinx says it is actively engaged with more than 100 customers on the UltraScale+ portfolio with design tools, and has already shipped devices and/or boards to over 60 of them. The devices join the Zynq UltraScale+ MPSoCs and Kintex UltraScale+ on 16nm. Virtex UltraScale+ devices are aimed at ...

Xilinx offers lower cost 28nm FPGA

Xilinx is offering the Spartan-7 family of FPGAs designed for I/O intensive applications. The Spartan-7 FPGAs will be supported on the Vivado Design Suite WebPACK Edition, freely downloadable, as well as the Vivado Design and System Editions. The new FPGAs are designed to provide energy and cost efficiency over previous generations when applied to interface bridging. The new family is optimised ...

Dev board puts ECP5 FPGAs in small cells

Lattice Semiconductor is targeting its ECP5 range of FPGAs at small cell wireless basestations and communications terminals and it has introduced a development kit for system prototyping and test. The ECP5 Versa development kit allows designers to evaluate system performance against interface standards such as PCI Express, Gigabit Ethernet, DDR3 and generic SERDES. Lattice has also created a version of its Diamond software ...

China launches FPGA family

Twenty-month-old Gowin Semiconductor of Guangdong has a two-device family of FPGAs called GW1N – GW1N-1K and GW1N-9K. They are made on TSMC’s 55nm process with an embedded flash block which can be randomly accessed. According to Gowin they have up to 9K LUTs; up to 198K embedded block SRAM bits and nearly 20K Shadow SRAM bits; up to 2 million ...

Zynq UltraScale+ gets Micrium RTOS for all processors

Xilinx’s All Programmable Zynq UltraScale+ MPSoC has been supported by a commercial real-time operating system (RTOS) from Micrium. The Zynq UltraScale+’s quad-core ARM Cortex A53 and dual-core Cortex R5 CPUs will run the Micrium µC/OS-II, µC/OS-III kernels and full suite of RTOS components, the company says. They will also run on the Xilinx MicroBlaze FPGA-based soft processor core which can ...

Cypress gives Bluetooth platform memory for OTA downloads

Cypress Semiconductor has doubled the memory capacity on its Bluetooth Low Energy enabled PSoC 4 and PRoC programmable radio-on-chip devices. The programmable devices now have 256kbyte of flash and 32kbyte of SRAM. The additional memory capacity is intended to support over-the-air (OTA) firmware upgrades. The PSoC’s development IDE called Creator supports the Bluetooth Low Energy configurations. The devices integrate a ...

Electronics Weekly Electronics Design & Components Tech News

Electronics Weekly Electronics Design & Components Tech News