Such fine-grained die-to-wafer interconnects pave the way to logic/memory-on-logic and memory-on-memory applications. On the longer term, die-to-wafer bonding will enable also die- and wafer-level optical interconnects – for which imec demonstrated a first proof of concept at ECTC2024.

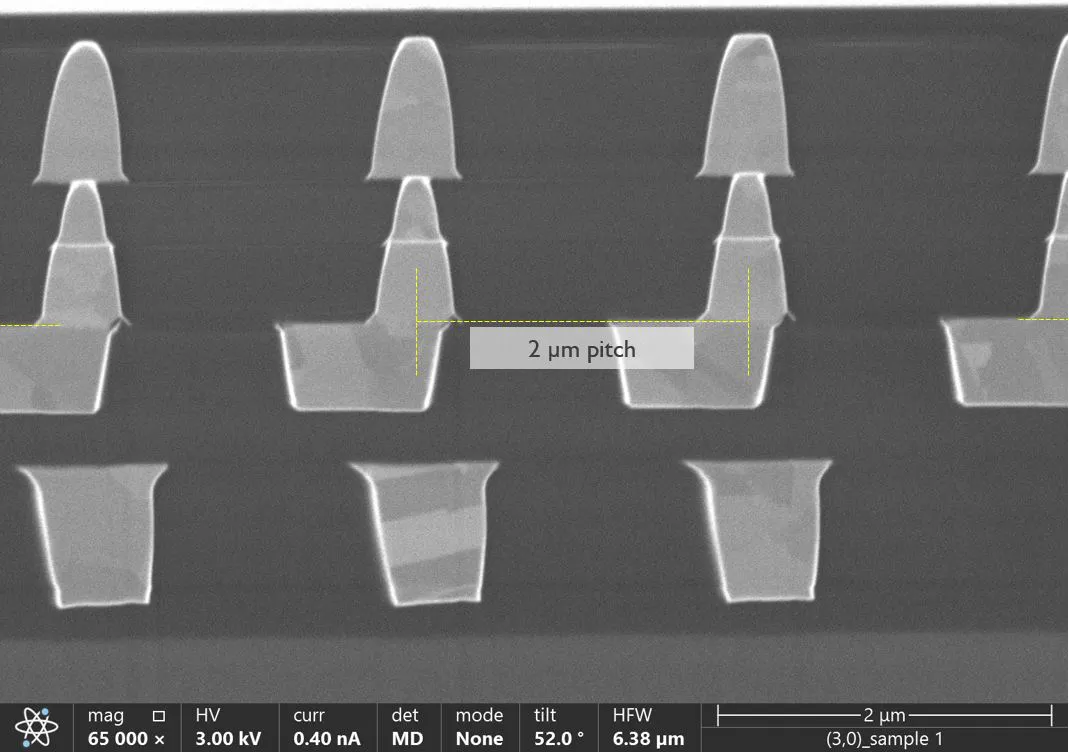

Imec is developing a process flow for direct die-to-wafer hybrid bonding at interconnect pad pitches well below 10µm, down to 1µm. To reach these goals, imec achieved a major process improvement, in particular preserving ultraclean surfaces during processing, die singulation and pick-and-place; and maintaining a high throughput during all the process steps. This has led to a first demonstration with a Cu bond pad pitch scaling down to 2µm.

Hybrid bonding requires very high-quality surface preparation to achieve smooth surfaces with minimal Cu pad recess (<2.5nm), requiring careful optimization of the chemical-mechanical polishing (CMP) step of the Cu/SiCN surface.

These properties need to be maintained during wafer singulation and die-to-wafer placement. To achieve a high-quality die singulation, without particles and impact to the Cu/SiCN surface, a plasma dicing process was implemented.

Critical to the pad pitch scaling is a fast but high accuracy pick-and-place step. The die processing together with a high-accuracy pick-and-place step resulted in <350nm die-to-wafer overlay errors. The assembly flow enabled 2µm pitch Cu bond pads with good electrical yield: Kelvin e-yield >85% and daisy chain e-yield >70%.

Eric Beyne, senior fellow, VP of R&D, and program director 3D system integration at imec said: “In terms of interconnect pitch, die-to-wafer hybrid bonding can now bridge the gap between solder-based die-to-wafer bonding (which is likely to stagnate at 10 to 5µm bump pitch) and wafer-to-wafer hybrid bonding (allowing interconnects well below 1µm, down to 400nm pitch (as presented at IEDM 2023), and possibly 200nm pitch in the future). Compared to the latter, die-to-wafer bonding offers the advantage of stacking only known-good dies (resulting in higher compound yields) and of bonding dies of unequal size. Future improvements to our process flow will further push the interconnect pitch towards 1µm. With this evolution, die-to-wafer bonding can enter the realm of memory/logic-on-logic and memory-on-memory stacking.”

In addition, high-precision die-to-wafer bonding processes are a key enabler for wafer-level optical interconnects – imec’s long-term vision for high-bandwidth, low-power connections between multiple compute chips (xPUs) and high-bandwidth memory (HBM) in AI/ML clusters.

An attractive approach from cost and yield perspective is to partition the optical interconnect in a passive optical interconnect wafer, containing long-range routing waveguides and passive optical functions, and active photonic IC (PIC) dies (with modulators and photodetectors) – which in turn are bonded to an electrical IC (XPU or HBM).

Van Campenhout, fellow and R&D program director at imec said: “As a first proof of concept, we enabled low-loss evanescent optical coupling between PIC dies and a 300mm bottom optical interconnect wafer – leveraging a (collective) SiCN dielectric-based die-to-wafer assembly process. Benefitting from the accurate die-to-wafer alignment, low optical coupling losses of below 0.5dB were obtained. In the next steps, we will expand our assembly flow – e.g. by also providing Cu-to-Cu interconnects throughout the die-to-wafer stack.”

Electronics Weekly Electronics Design & Components Tech News

Electronics Weekly Electronics Design & Components Tech News