At DAC 2024, Altair showcased its 3D-IC design and SimLab multi-physics modelling and simulation tool. Today, the company has announced the acquisition of Metrics Design Automation, a Canadian company led by Joe Costello , former CEO of Cadence Design Systems (1988-1997). The company described DSim as a full feature System Verilog and VHDL RTL simulator. It enables designers to simulate ...

Tag Archives: EDA tools

NoC design tool is cloud-based

DAC 2024: Believed to be the first cloud-based NoC (network on chip) design tool, the iNoCulator is available on an early access basis from SignatureIP. Today, there is a need to design multiple chipets and design scalable designs with chiplet-based systems, explained Purna Mohanty, CEO of SignatureIP. As the interconnect between compute, storage, memory and I/O blocks on a chip, ...

Focus shifts for HDL workflow in chiplet era

DAC 2024: The need to organise HDL hardware description language) tools in an era of chiplet design and higher abstraction and higher synthesis levels, Sigasi has introduced its Visual HDL portfolio, designed to correct inefficient HDL-based design workflows and reduce the number of iterations needed. The Belgium company explained that SVH (Sigasi Visual HDL) is an IDE (integrated development environment) ...

DVCon USA 24-27 February 2025

DVCon 2025 is a highly technical conference for design and verification with discussions on the latest technologies and how they can be adopted for projects and designs.

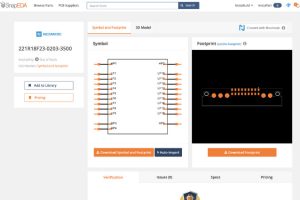

EDA models for 2mm pitch high-rel connectors

Nicomatic has contracted SnapEDA to provide CAD models for two-row versions of Nicomatic’s CMM 220 and 320 micro connector series – a total of over eight million variants. “Options range from 4 to 60 for signal contacts and 4 to 54 for coaxial or power contacts with locking or racking fixings,” according to SnapEDA. “To generate the parts, engineers need ...

Simulation model certified for functional safety Risc-V core

Risk-V intellectual property company Andes Technology has certified simulation reference models from Imperas reference for use evaluating multi-core designs featuring the functional-safety-optimised AndesCore N25F-SE. At the same time, it also certified the complete range of Andes processor IP blocks with ‘Andes Custom Extension’ (ACE) support. Such virtual references run exactly the same binary code as any resulting hardware would. “Functional ...

Cadence: IC design tool speeds sign-off

Cadence has announced a design tool for IC design sign-off. Called Certus closure solution, the “environment automates and accelerates the complete design closure cycle, from sign-off optimisation through routing, static timing analysis and extraction”, said Cadence. “The solution supports the largest chip design projects with unlimited capacity.” It lists these attributes: Distributed hierarchical optimisation and sign-off architecture for cloud and ...

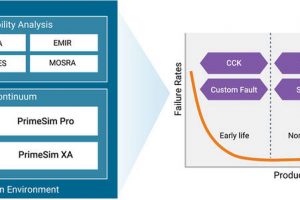

Synopsys unifies its reliability analysis workflow

Synopsys has unified the workflow through its existing reliability analysis tools for analogue, mixed-signal and custom IC designs – integrating them into its PrimeWave design environment, along with PrimeSim Continuum that announced in April. The unified workflow is to be called PrimeSim Reliability Analysism and is an umbrella for its CKK, Custom Fault, AVA, SPRES, EMIR and MOSRA tools (see table ...

C++ synthesis suite for PolarFire FPGA algorithm development

Microchip has released a C++ algorithm high-level synthesis design workflow for its PolarFire FPGAs. “A large majority of edge compute, computer vision and industrial control algorithms are developed natively in C++ by developers with little or no knowledge of underlying FPGA hardware,” according to the company. Called SmartHLS, the tool allows C++ algorithms to be directly translated to FPGA-optimised RTL ...

Andes certifies Risc-V SIMD and DSP reference models

Risc-V core design house Andes Technology has certified reference models for its cores with ‘P’ extensions from Imperas. Cores carrying the P designation have SIMD and DSP extensions to the instruction set for data processing and real-time operation. “The RISC-V International P Extension Task Group is in the final stages of submitting the specification to the official ratification process, which ...

Electronics Weekly Electronics Design & Components Tech News

Electronics Weekly Electronics Design & Components Tech News