Cadence Design Systems has announced its work with TSMC in 5nm and 7nm+ FinFET chip design for mobile devices.

Cadence said its digital, sign-off and custom/analogue tools have achieved the latest Design Rule Manual (DRM) and SPICE certification for the silicon foundry’s 5nm and 7nm+ processes.

Cadence said its digital, sign-off and custom/analogue tools have achieved the latest Design Rule Manual (DRM) and SPICE certification for the silicon foundry’s 5nm and 7nm+ processes.

Cadence will presents details of the work with TSMC at the CDNLive EMEA 2018 event which takes place from May 7- 9 in Munich at the Infinity Hotel & Conference Resort.

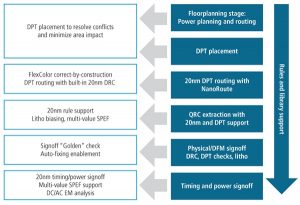

The tool firm provides an integrated digital flow from implementation to final sign-off that has been certified by TSMC.

For the 7nm+ process, the flow includes the Innovus Implementation System, Quantus Extraction Solution, Tempus Timing Signoff Solution, Voltus IC Power Integrity Solution, Physical Verification System (PVS) and Layout-Dependent Effect (LDE) Electrical Analyser.

For the 5nm process, the Cadence certified tools include the Innovus Implementation System, Quantus Extraction Solution, Tempus Timing Signoff Solution, Voltus IC Power Integrity Solution, Voltus-Fi Custom Power Integrity Solution, the layout vs. schematic (LVS) function in PVS and LDE Electrical Analyser.

Cadence digital and sign-off features available for the 7nm process are also available for the 5nm and 7nm+ process.

Some of these features include cut-metal handling throughout the design flow, via-pillar support, clock mesh and bus-routing. These capabilities can enable customers to successfully design mobile and HPC systems with improved power, performance and area (PPA) while reducing iterations and achieving their cost and performance objectives.

There are also tool enhancements focused on EUV support at key layers and associated new design rules that specifically support the 5nm and 7nm+ processes. Some of the other newest enhancements for the 7nm+ process include cell pin support, Self-Heating Effect (SHE) and heatsink support.

And for the 5nm process, the sign-off tools offer high-resistance resistor support, router compliance for new rules and new extraction support including additional resistor layer modelling and other middle end-of-line (MEOL) features.

Electronics Weekly Electronics Design & Components Tech News

Electronics Weekly Electronics Design & Components Tech News