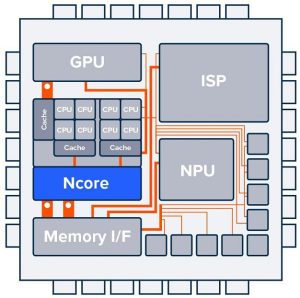

“In 2020, Arteris announced a partnership with Arm and the alignment of our roadmaps to support CHI-E and ASIL B and ASIL D safety,” Arteris told Electronics Weekly. “We confirm the expansion of that partnership with a pre-validation of our Ncore interconnect intellectual property with Armv9 cores. Ncore is ready to meet ISO 26262 requirements from ASIL B to ASIL D for automotive and other mission-critical systems.”

CHI-E is a protocol AMBA busses, and it joins CHI-B and ACE AMBA protocols already in Ncore, and ACE-Lite for IO coherency, as well as AXI. “Ncore enhances AXI’s capabilities, enabling it to interact with CPU caches as if IO coherency were native to it,” claimed Arteris.

Upgraded in Ncore v3.6 are replacement policies for caches, which now includes PLRU (pseudo least recently used) and NRU (not recently used).

Debug interfaces have been upgraded to AMBA APB4, and Ncore’s functional safety control now supports parity bits protecting registers.

Multi-cycle SRAMs are supported and there is a fourth control network to improve read and write bandwidth.

“SoC designers are challenged by the growing complexity resulting from the number of processing elements, multiple protocols and functional safety requirements of modern electronics,” said Arteris CEO Charles Janac. “Our latest release of Ncore marks an important milestone towards our ultimate vision to connect any processor, using any protocol and topology.”

Electronics Weekly Electronics Design & Components Tech News

Electronics Weekly Electronics Design & Components Tech News