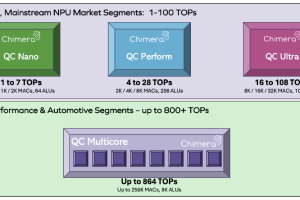

The third generation of general-purpose neural processing units (GPNPUs) by Quadric introduces pre-integrated clusters of two, four or eight cores to deliver up to 108 TOPS. This latest iteration has increased performance and optimisations for generative AI. the company has also introduced a safety enhanced version for automotive applications. The company described the Chimera QC series as NPUs with a ...

Tag Archives: SoC

Focus shifts for HDL workflow in chiplet era

DAC 2024: The need to organise HDL hardware description language) tools in an era of chiplet design and higher abstraction and higher synthesis levels, Sigasi has introduced its Visual HDL portfolio, designed to correct inefficient HDL-based design workflows and reduce the number of iterations needed. The Belgium company explained that SVH (Sigasi Visual HDL) is an IDE (integrated development environment) ...

mmWave updates gear up for automotive growth

A two-chip cascading imaging radar system has been unveiled by Calterah, based on 6T-6R mmWave radar SoCs from Andes Technology. The 22nm CMOS SoCs, which will be available from June 2024, integrate an RF module and include a quad-core CPU with a DSP and proprietary radar signal processor. Flex-Cascading allows the two SoCs to be cascaded through chip-to-chip interfaces. This ...

Skills report on chip industry

The METIS (MicroElectronics Training, Industry and Skills) study has concluded and finds that the Top Five Critical Job Profiles in the microelectronics sector in 2023 are: Data specialist Software engineer Design engineer Process engineer Maintenance technician The Top Emerging Skills in 2023 are: Machine Learning and Artificial Intelligence Data Analysis Systems Design and System Architecture (SoC, SiP, SoP, complex ASIC) ...

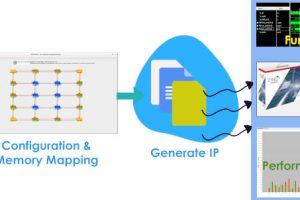

Try a network-on-chip configuration tool?

SignatureIP is offering a trial of its processor agnostic network-on-chip (NoC) configuration software. Called iNoCulator, the “tool enables users to find the optimal NoC configuration, and the company believes that it is the fastest on the market”, it said. “This try-before-you-buy offer will enable engineers to see for themselves just how easy it is to design a NoC with our tool.” ...

Renesas moves to chiplets for automotive processors

Renesas will be using chiplets in its next generation of automotive SoCs, and will add software and tool-compatible automotive microcontrollers. The company revealed this when announcing its 5th generation ‘R-Car’ product range, the first of which will be sampling late next year for cars shipping in 2027. Chiplets are simply die to be used inside multi-die packages. They increase product ...

Sponsored Content: Calterah, Leading Chinese mmWave IC Provider, Brings Full Radar SoC Portfolio for ADAS and Autonomous Driving to IAA

As the curtain has just risen on IAA Mobility 2023 in Munich on September 5, the leading Chinese provider of CMOS mmWave radar chips, Calterah, brings a most comprehensive portfolio of automotive radar SoCs at Booth A2-F31 of Mess München to the global audience. Figure 1 Visitors Showing Great Interest in Calterah mmWave Radar SoCs (please click on images to ...

Phone processor for gaming and AI photography

MediaTek has announced some details of its Dimensity 7200 phone SoC. To be built on a 4nm process from TSMC, it will have eight Arm cores: two 2.8GHz Cortex-A715 cores and six Cortex-A510, then MediaTek’s own AI processing pnit (APU) and an Arm Mali G610 GPU. Memory runs at 6.4Gbit/s and there is UFS 3.1 for storage. For gamers, there ...

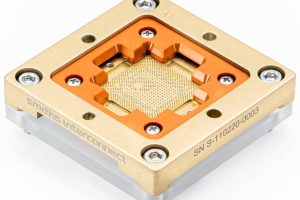

Test socket with less cross-talk for 350μm pitch ICs

Smiths Interconnect has created an IC test socket for high-speed testing of 350μm minimum pitch devices. Called DaVinci Micro, the test socket has shielded connections to isolate signal paths, with -35dB crosstalk claimed at 40GHz, as well as -10dB return loss at the same frequency and -1dB insertion loss at 31GHz. There are to impedance variants: 851-0023043-HG01 for 50Ω and ...

ST’s Bluetooth LE 5.2 chip supports concurrent connections to 128 nodes.

STMicroelectronics has introduced a third generation of Bluetooth chip, describing it as “the world’s first Bluetooth LE 5.2-certified SoC to support concurrent connections up to 128 nodes”. Called BlueNRG-LP, according o the company it can consume as little as 3.4mA in receive mode, 4.3mA when transmitting, and under 500nA when quietly waiting for wake-up events. RF output power is programmable ...

Electronics Weekly Electronics Design & Components Tech News

Electronics Weekly Electronics Design & Components Tech News