Versal AI and Versal Prime were introduced at the Developer Forum in response to the need for heterogeneous computing to process the volumes of data in use today.

“Versal is a disruptive technology,” said Kirk Saban, Senior Director, Product and Technical Marketing, at Xilinx at a pre-briefing.

“No one architecture prevails today; this is the era of heterogeneous compute,” he announced. “Today’s developers need software programmability, performance for diverse range of applications – they need to port and adapt code to give the best performance for an application. In this [the developers] are hardware agnostic”.

As result, said Saban, a platform is needed that can scale and keep pace with innovation.

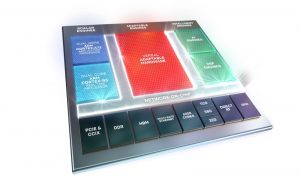

The AI Core series is designed to blend inference with adaptable scalable engines for adaptable workloads for the application, explained Saban. The series is optimised for cloud, networking, and autonomous technology and is made up of five devices with 128 to 400 AI Engines.

The devices are based on dual-core Arm Cortex-A72 application processors, dual-core Arm Cortex-R5 real-time processors. In addition to 1.9 million system logic cells, there are 32-Mbit of new Accelerator RAM blocks which support custom memory hierarchies.

PCIe Gen4 eight-lane and 16-lane, and CCIX host interfaces are provided, together with 32G SerDes, up to four integrated DDR4 memory controllers, up to four multi-rate Ethernet MACs and 650 high-performance I/Os for MIPI D-PHY, NAND, storage-class memory interfacing and LVDS.

A network on chip (NoC) has up to 28 master/slave ports, and delivers multi-Tbps bandwidth at low latency.

The Versal Prime series is the mid-range option in the portfolio and targets inline acceleration, as used in radar beam forming, for example. It is based on the same Arm cores as the AI Core and is made up of nine devices.

It has over 4,000 DSP engines, for high-precision floating point with low latency and over two million system logic cells, 200-Mbit of UltraRAM, more than 90-Mbit of block RAM and 30-Mbit of distributed RAM. The series also includes four- and eight-lane PCIe Gen4 and CCIX host interfaces, SerDes and 58G PAM4 SerDes, up to six integrated DDR4 memory controllers, up to four multi-rate Ethernet MACs, I/O for MIPI D-PHY, NAND, and storage-class memory interfaces, LVDS and HD I/O for 3.3V interfacing.

Target applications are communications test equipment, data centre network and storage acceleration, Nx100G Ethernet and optical transport networking (OTN), broadcast switches, medical imaging and avionic control.

The Versal series is based on TSMC’s 7nm FinFET process technology. The AI Core and Premium are with customers through Xilinx’s early access programme and will be generally available in the second half of 2019.

In his keynote, Xilinx CEO, Victor Peng, described Versal as “customised silicon without doing customised silicon – it’s scalable and extensible.”

The AI Core is designed for AI interference throughput while the Prime is the mid-range, broadest application, both available in 2019. In 2020, the company will introduce the Premium, with 112G SerDes and 600G core and the AI Edge, the lowest power AI family. Later in 2020, the AI RF will be introduced. This has integrated RF for 5G wireless applications. In 2011, the HBM option, for memory integration, will be introduced.

here is a development environment to enable Versal. Its software stack includes drivers, middleware, libraries and software framework support. Software programming tools will be announced next year.

Electronics Weekly Electronics Design & Components Tech News

Electronics Weekly Electronics Design & Components Tech News

OK, so what is the timeline for sampling, development tools, GA, etc???