Akeana has announced a little about its RISC-V processor intellectual property. There will be three series: 100 Series – configurable 32bit RISC-V cores for embedded microcontrollers 1000 Series – includes 64bit RISC-V cores and a memory management unit, optional support for multi-threading and extensions including: vector, hypervisor and AI computation. 5000 Series – 64bit RISC-V cores optimised for laptops, data ...

Tag Archives: intellectual property cores

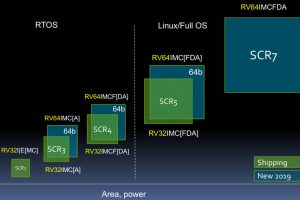

RISC-V Summit: SiFive’s 4th generation embedded cores

SiFive announced the 4th generation of RISC-V CPU cores for embedded applications at RISC-V Summit Europe 2024 today. There are eight cores, three of which are 32bit while the other five are 64bit. To trade performance against power and area, their pipelines will span two-stage single-issue, to eight-stage dual-issue – see the table below. They are all covered by the ...

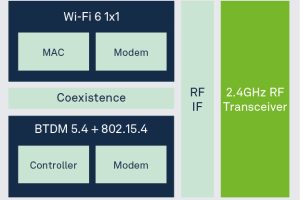

IP block covers Wi-Fi 6, Bluetooth 5.4 dual mode and IEEE 802.15.4 for IoT chips

Ceva has introduced a multi-radio intellectual property package for IoT IC designers that combines Wi-Fi 6, Bluetooth 5.4 and 802.15.4 modems with a 2.4GHz transceiver aimed at TSMC’s 22nm process. Called Links100 (diagram right), it is the first of a series of IP products (diagram below) that will also include transceivers for Wi-Fi 7 with MLO (multi-link operation), and UWB ...

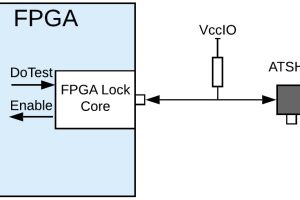

IP block secures FPGAs with one external IC

Protecting against IP theft, and to prevent contract manufacture hardware counterfeiting, ‘FPGA Lock’ from Nial Stewart Developments is an intellectual property block for FPGAs that communicates with Microchip’s SOT-23 ATSHA204A crypo-authentication IC. The cores uses generic Intel altsyncram and Xilinx 7 series blockram macros and occupies ~720 registers and two ram blocks. Only one pin on the FPGA is needed, ...

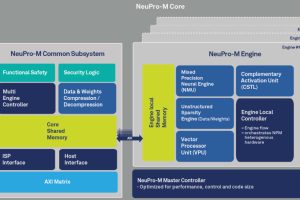

Ceva adds cores and generative AI to neural processing IP portfolio

Ceva has filled-out its NeuPro-M family of neural processing units, and boosted its architecture for generative AI algorithms. “NeuPro-M NPU architecture and tools have been redesigned to support transformer networks in addition to convolutional neural networks,” according to the company. “This enables applications leveraging the capabilities of generative and classic AI to be developed and run on the NeuPro-M NPU.” ...

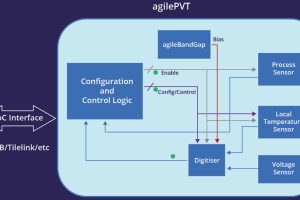

Analogue IP blocks are pre-wrapped in digital logic to ease integration

Cambridgeshire-based IC design intellectual property company Agile Analog has created a range of analogue peripheral blocks that are already wrapped in digital logic to connect them to a standard on-chip bus, such as AMBA APB. The aim is to “reduce the effort required to integrate multiple analogue IPs into any asic by allowing the IP to be dropped straight into ...

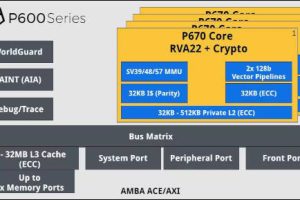

High-performance RISC-V cores from SiFive

SiFive has announced two high-performance RISC-V processing cores. “P670 and P470 are specifically designed for the most demanding workloads for wearables and other advanced consumer applications,” said SiFive v-p Chris Jones. “We have optimised these RISC-V Vector-enabled products to deliver performance and efficiency improvements and we are in evaluations with a number of top-tier customers.” Both are also available in ...

Risc-V day: Syntacore for Risc-V MCU core IP

Syntacore has been developing processor core IP based around the Risc-V instruction set for four years

Imagination and GF collaborate to put low power wireless on SoCs

Imagination Technologies and Global Foundries are to collaborate to offer low-power baseband and RF functions – Bluetooth Low Energy and IEEE 802.15.4, for example – to mutual customers. The deal combines Imagination’s Ensigma radio IP with 22FDX from GF – its 22nm FD-SOI process. “22FDX is an appealing option for customers designing cost-sensitive devices,” said Imagination executive v-p of marketing ...

Altera offers FPGA cores for 40GbE and 100GbE

These cores can be used for building systems requiring very high throughput-rate standard Ethernet connections, including chip-to-optical module, chip-to-chip,

Electronics Weekly Electronics Design & Components Tech News

Electronics Weekly Electronics Design & Components Tech News