Akeana has announced a little about its RISC-V processor intellectual property. There will be three series: 100 Series – configurable 32bit RISC-V cores for embedded microcontrollers 1000 Series – includes 64bit RISC-V cores and a memory management unit, optional support for multi-threading and extensions including: vector, hypervisor and AI computation. 5000 Series – 64bit RISC-V cores optimised for laptops, data ...

Tag Archives: Intellectual Property

AI processor intellectual property aimed at TinyML

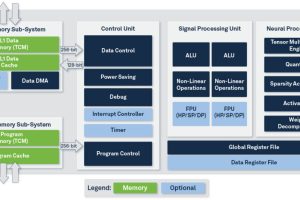

Ceva has announced a neural network processing core aimed at SoCs needing to run TinyML models. There are two versions: NPN32 with 32 int8 MACs NPN64 with 64 int8 MACs “Both of which benefit from Ceva-NetSqueeze for direct processing of compressed model weights,” according to the company. “NPN32 is optimised for most TinyML workloads targeting voice, audio, object detection and ...

Arm’s most powerful neural processor for microcontrollers

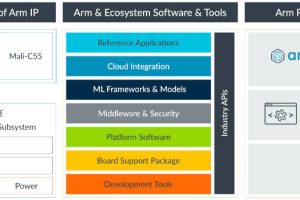

Arm has announced its most powerful microcontroller-grade neural processor, which will reach 4Top/s in its maximum configuration and is 20% more power efficient that its previous neural processors. Named Ethos-U85 and configurable with between 128 and 2,048 MACs, it is intended to have enough performance to locally run heavy AI algorithms such as ‘transformers’, as well as convolutional neural networks. ...

Semidynamics proposes modular RISC-V architecture for scalable AI processing

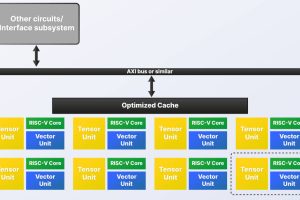

Barcelona-based Semidynamics is aiming at next-generation AI chips and algorithms such as transformer with intellectual property called ‘All-In-One AI’. Rather than having on the same IC a multi-core CPU, a multi-core GPU for vector processing and a multi-core neural processor for tensor processing, it is advocating multiple instances of a block consisting of one out-of-order 64bit RISC-V CPU, one (GPU-like) ...

Accelerated RISC-V core optimised for edge AI and cryptography

Red Semiconductor has announced RISC-V instruction set extensions, and a hardware design, for edge AI and cryptography in asics and FPGAs. The hardware, called ‘VISC’, is an accelerated RISC-V core that “optimises complex mathematical algorithms for parallel execution in its reconfiguration hardware engine”, according to Red, which claims: “The VISC ISA [instruction set] enables developers to describe complex algorithms in ...

Network-on-chip supports Arm v9 and automotive functional safety

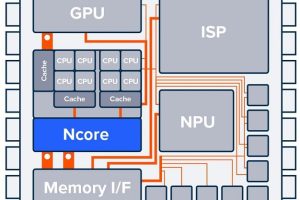

Arteris is supporting Armv9 automotive cores and ASIL D functional safety with release 3.6 of its Ncore cache coherent network-on-chip. “In 2020, Arteris announced a partnership with Arm and the alignment of our roadmaps to support CHI-E and ASIL B and ASIL D safety,” Arteris told Electronics Weekly. “We confirm the expansion of that partnership with a pre-validation of our ...

Ceres licences fuel cell technology to Delta

Delta Electronics has signed a technology transfer and licensing collaboration agreement with Ceres Power, paying ~£43m to access Ceres’ hydrogen stack technology for solid oxide fuel cells (SOFCs) and solid oxide electrolysis cells (SOECs). “Through this partnership, Delta expects to integrate Ceres’ energy stack technology with its own power electronics and thermal management technologies to develop SOFC and SOEC systems ...

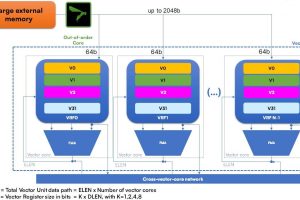

RISC-V Summit: Customisable vector unit

Semidynamics has announced a customisable vector unit for RISC-V processor cores, compliant with RISC-V vector specification 1.0. Vector unit are composed of several vector cores that perform multiple calculations in parallel. In this case, Semidynamics’ vector core can be tailored to support FP64, FP32, FP16, BF16, INT64, INT32, INT16 or INT8 data types depending on requirements – the longest word-length ...

LPDDR5X interface IP works up to 8.55Gbit/s

Cadence Design Systems has announced LPDDR5X memory interface intellectual property designed to operate at 8,533Mbit/s, claiming it to be the first. Based on its LPDDR5 and GDDR6 products, the IP has a PHY and a controller, designed to follow the JEDEC JESD209-5B standard. The controller-PHY interface is based on the latest DFI 5.1 specification, and a variety of on-chip buses ...

Post-quantum cryptographic IP from Xiphera

Xiphera has announced intellectual property cores for implementing hardware post-quantum cryptography security on FPGAs and asics. Such security is executed on classical computing platforms to protect against quantum computing based attacks. Branded ‘xQlave’, the IP blocks are aimed at quantum-secure key exchange and digital signatures. “Powerful enough quantum computers will be able to break current public-key asymmetric cryptosystems based on ...

Electronics Weekly Electronics Design & Components Tech News

Electronics Weekly Electronics Design & Components Tech News