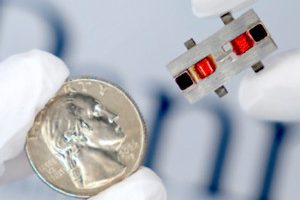

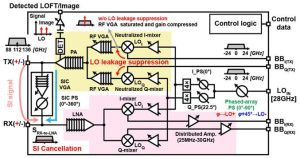

Capable of transmission and reception at over 100GHz, and at 112Gbit/s, “by effectively suppressing the self-interference caused by the transmission signal leaking into the receiver, the proposed architecture reaches unprecedented data rates while maintaining a surprisingly compact size”, according to Tokyo Tech.

The aim is single-antenna full-duplex communication in a postulated 88 to 136GHz (‘sub-THz’) 6G band.

“Single-antenna full-duplex architectures suffer greatly from self-interference,” said the university. “Such systems must include circuits for self-interference cancellation that attempt to cancel the generated interference by injecting an equal signal with the opposite polarity.”

The Tokyo Tech system has a dual-polarised patch antenna driven by a combination of positive and negative feeding ports for transmission and reception. Mismatch of the transmitted signal that leaks into the differential receiver’s ports is minimised by concentrating on the symmetry of the ports’ circuit paths.

“Our design avoids large transmission leakages prevalent in devices with asymmetric antenna structures and asymmetric differential signal ports,” said research team head Professor Kenichi Okada.

Due to limited phase range and poor resolution in the sub-THz band, the internal self-interference cancellation circuit avoids tuning by conventional varactors.

Instead, the team claims to have developed a new varactor structure “that achieved excellent linear resolution over the entire sub-THz band, and over the full 360°”, it said.

“In the over-the-air measurement, the proposed full-duplex transceiver achieved 6Gbit/s,” said Okada. “Self-interference suppression was improved by 20dB when the canceller was turned on.”

For more details, ‘A Sub-THz full-duplex phased-array transceiver with self-interference cancellation and LO feedthrough suppression’ will be presented at Symposium on VLSI Technology and Circuits in Kyoto next week (11 – 16 June).

Electronics Weekly Electronics Design & Components Tech News

Electronics Weekly Electronics Design & Components Tech News