Memory access is important with neural network algorithms as their execution requires large quantities of data to be transferred between processing elements and memory, increasing emphasis on the performance of the access link.

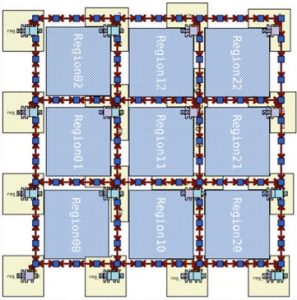

The partnership is to make Arteris’ FlexNoC and Ncore network-on-chip development environment work with Fraunhofer IESE’s DRAMSys memory subsystem design framework.

“Early, accurate modelling of the characteristics of DRAM architectures is a critical component to arrive at power-optimised SoC architectures,” according to Professor Matthias Jung of Fraunhofer IESE. “By enabling interoperability and integration between Arteris’ FlexNoC and Ncore with DRAMSys4.0, our customers can understand the impact of advanced DRAM technology on network-on-chip performance and power consumption at the earliest project stages.”

Electronics Weekly Electronics Design & Components Tech News

Electronics Weekly Electronics Design & Components Tech News