These modules are described as “end-user friendly hot pluggable assemblies” and are for data centres and similar server applications. They conform to SNIA (Storage Networking Industry Association) EDSFF form factors E1.S and E3.S.

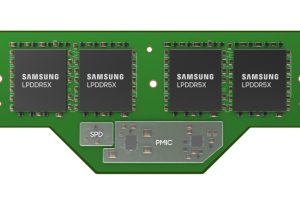

CXL

Specifically, JESD405-1B defines the contents of labels for such CXL Memory Modules (CMMs). These labels include information about the memory media type (such as DDR5), the revision level of the supported Compute Express Link protocol, and total capacity in gigabytes or terabytes. There is also information about support for connector and I/O configurations from a x4 to x16 over a single connector (1C) through four connectors (4C).

Release version 1.1 includes documentation for the country of origin of the module assembly readable in the required 2D barcode, which aims to simplify inventory management.

JESD317A

JESD405-1B joins “JESD317A (JEDEC Memory Module Reference Base Standard – for Compute Express Link (CXL) V1.0” – introduced in March 2023 – in defining the function and configuration of memory modules that support the CXL specifications.

“Both JESD317A and JESD405-1B affirm JEDEC’s active support for expanding the market for CXL solutions. These documents represent the cooperation of dozens of companies representing suppliers and end users of CXL memory solutions,” said Mian Quddus, JEDEC Board of Directors Chairman.

“End users can be assured of a multiplicity of sources for [CMMs], helping to commoditize these solutions for the good of the industry.”

Note that both JESD405-1B and JESD317A were developed in coordination with the Compute Express Link standards organisation.

Both standards are available for free download from the JEDEC website.

Image: Micron – CMMs

See also: JEDEC JEP30 specs Part Model Guidelines for Chiplet Integration

Electronics Weekly Electronics Design & Components Tech News

Electronics Weekly Electronics Design & Components Tech News